## i.Core STM32MP1

i.Core STM32MP1 is based on the new STM32MP157 processor from ST® equipped with a dualcore Cortex®-A7 and Cortex-M4. The new module offers very high performance, real-time capabilities, and low-power operation. The wide range of peripherals makes this SOM suitable for many different applications.

### **FEATURES**

#### HIGHLIGHTS

- Powerful dual core Cortex A7+Cortex M4

- Low Power Consumption

- · Suitable for a fan-less application with high-end

#### **APPLICATIONS**

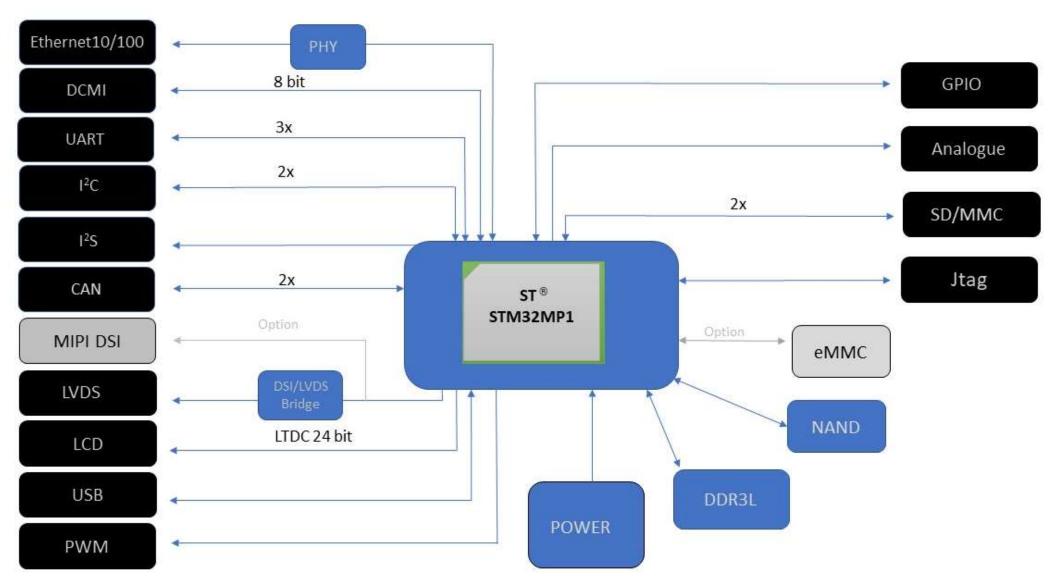

ST® STM32MP157

CORES

Dual-Core Cortex-A7 @650/800MHz and Cortex M4@200MHz

**MEMORY**

Up to 1GB LPDDR3L

3D GPU: Vivante®-OpenGL® ES2.0 - Up to 26 Mtriangle/s, 133 Mpixel/s LCD-TFT controller, up to 24-bit // RGB888 - up to WXGA (1366x768) @60 fps - Two layers with programmable colour LUT MIPI® DSI data lanes up to 1GHz each

- · LCD-TFT controller, up to 24-bit up to parallel RGB888

- MIPI®DSI 2 data lanes up to 1GHz each

- LVDS Single channel via MIPI-DSI bridge

**VIDEO PROCESSING**

Up to WXGA (1366x768) @60fps

**AUDIO**

I<sup>2</sup>S interface

PRINCE LAN 10/100 Ethernet interfaces

USB

• 1x USB HOST 2.0 1x USB OTG 2.0

MASS

· 512MB expandible Nand Flash

STORAGE

· 4GB eMMC drive soldered on-board

UART, I2C, SPI, CAN Bus, PWM, SDIO i/f, JTAG i/f

**POWER** SUPPLY

+5V DC

**OPERATING**

Linux · Yocto

**OPERATING** TEMPERATURE\*

Industrial and consumer qualified

**DIMENSIONS**

67,6 x 32,1 mm

\* Valid for all components except CPU. Customer shall consider junction temperature for CPU. Temperature will widely depend on application. Specific cooling solutions could be necessary for the final system.

# i.Core STM32MP1

## **BLOCK DIAGRAM**